# CS221: Logic Design

# Instructors: Dr. Ahmed Shalaby <u>http://bu.edu.eg/staff/ahmedshalaby14#</u> Dr. Fatma Sakr

# **Digital Fundamentals**

# CHAPTER 7 Latches, Flip-Flops and Timers

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

- S-R (Set-Reset) latch

- Gated S-R latch

- Gated D latch

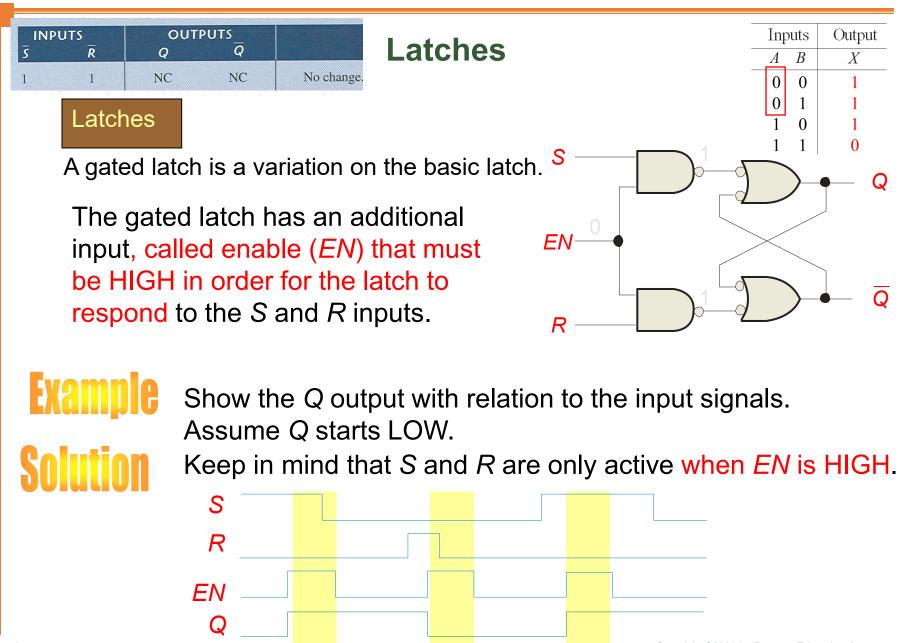

#### Latches

A **latch** is a **temporary storage device** that has two stable states (bistable). It is a **basic form of memory**.

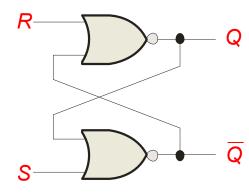

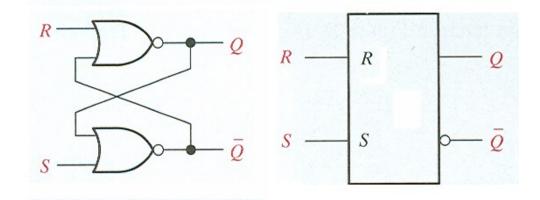

The S-R (Set-Reset) latch is the most basic type. It can be constructed from NOR gates or NAND gates.

With NOR gates, the latch responds to active-HIGH inputs. With NAND gates, the latch responds to active-LOW inputs.

NOR Active-HIGH Latch

NAND Active-LOW Latch

# Active-HIGH S-R Latch

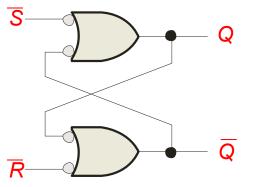

The active-HIGH S-R latch is in a stable (latched) condition when both inputs are LOW.

Assume the latch is initially **RESET** (Q = 0) and the inputs are at their inactive level (0).

To SET the latch (Q = 1), a momentary HIGH signal İS applied to the S input while the R remains LOW.

To RESET the latch (Q = 0), a momentary HIGH signal is applied to the *R* input while the S remains LOW

Never apply an active set and reset at the same time (invalid). Digital Fundamentals, 9/e

Floyd

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Output

Inputs

A

B

# Active-HIGH S-R Latch

| INPUTS |   | OUTPUTS |    |                                            |

|--------|---|---------|----|--------------------------------------------|

| 5      | R | Q       | Q  | COMMENTS                                   |

| 0      | 0 | NC      | NC | No change. Latch remains in present state. |

| 0      | 1 | 0       | 1  | Latch RESET.                               |

| 1      | 0 | 1       | 0  | Latch SET.                                 |

| 1      | 1 | 0       | 0  | Invalid condition                          |

2000000

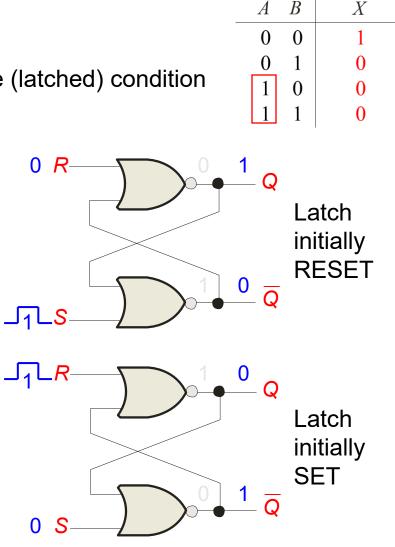

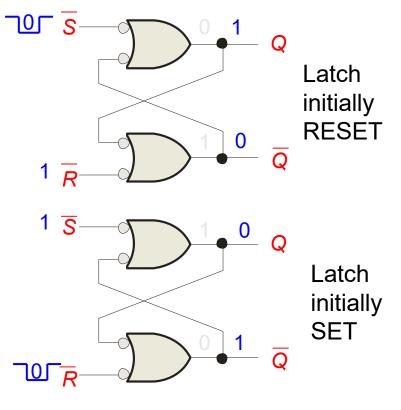

## Active-LOW S-R Latch

The active-LOW  $\overline{S}-\overline{R}$  latch is in a stable (latched) condition when both inputs are HIGH.

Assume the latch is initially RESET (Q = 0) and the inputs are at their inactive level (1).

#### To SET the latch (Q = 1), a momentary LOW signal is applied to the $\overline{S}$ input while the $\overline{R}$ remains HIGH.

To **RESET the latch (Q = 0)** a momentary LOW is applied to the  $\overline{R}$  input while  $\overline{S}$  is HIGH.

Never apply an active set and reset at the same time (invalid).

Floyd Digital Fundamentals, 9/e

| Inp | uts | Output |

|-----|-----|--------|

| A   | В   | X      |

| 0   | 0   | 1      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 0      |

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

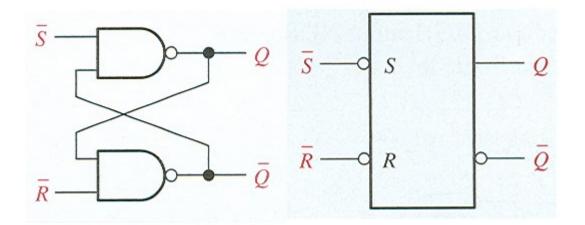

# Active-LOW S-R Latch

| INPUTS            |   | OUTPUTS |    |                                            |  |  |

|-------------------|---|---------|----|--------------------------------------------|--|--|

| <u>s</u> <u>R</u> |   | Q       | Q  | COMMENTS                                   |  |  |

| 1                 | 1 | NC      | NC | No change. Latch remains in present state. |  |  |

| 0                 | 1 | 1       | 0  | Latch SET.                                 |  |  |

| 1                 | 0 | 0       | 1  | Latch RESET.                               |  |  |

| 0                 | 0 | 1       | 1  | Invalid condition                          |  |  |

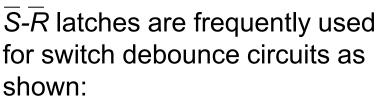

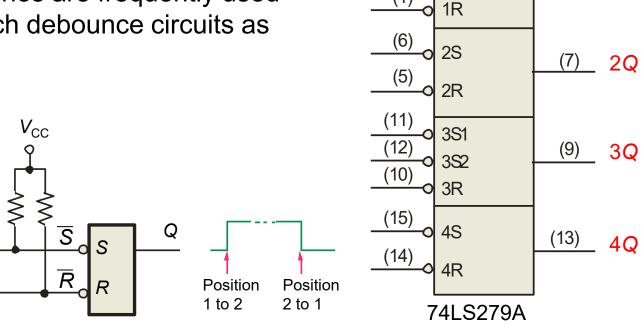

#### Latches

2

The active-LOW S-R latch is available as the 74LS279A IC.

1S1

1S2

(3)

(1`

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

(4)

1Q

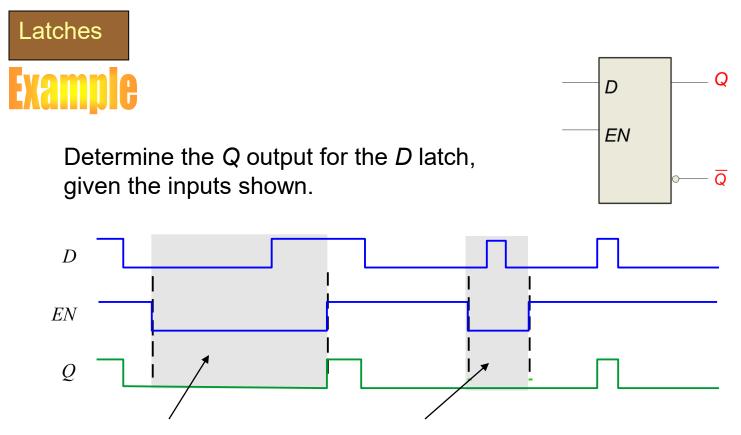

#### Latches

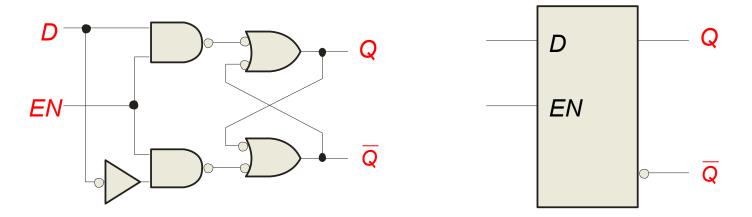

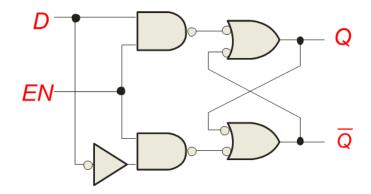

The *D* latch is an variation of the *S*-*R* latch but combines the *S* and *R* inputs into a single *D* input as shown:

#### A simple rule for the *D* latch is:

*Q* follows *D* when the Enable is active.

#### Latches

The truth table for the *D* latch summarizes its operation.

If *EN* is LOW, then there is no change in the output and it is latched.

| In          | Inputs      |                          | outs         |                           |

|-------------|-------------|--------------------------|--------------|---------------------------|

| D           | EN          | Q                        | Q            | Comments                  |

| 0<br>1<br>X | 1<br>1<br>0 | 0<br>1<br>Q <sub>0</sub> | 1<br>0<br>Q0 | RESET<br>SET<br>No change |

\_\_\_\_\_ D \_\_\_\_ Q \_\_\_\_\_ EN \_\_\_\_ Q

> Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Notice that the Enable is not active during these times, so the output is latched.

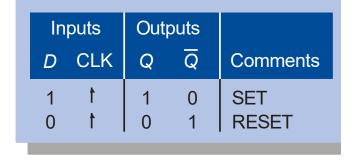

- Edge-triggered D flip-flop

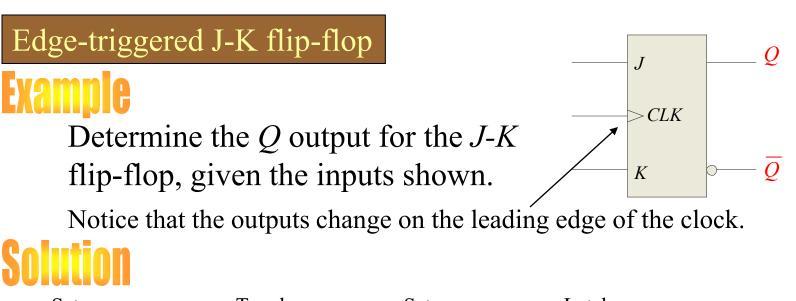

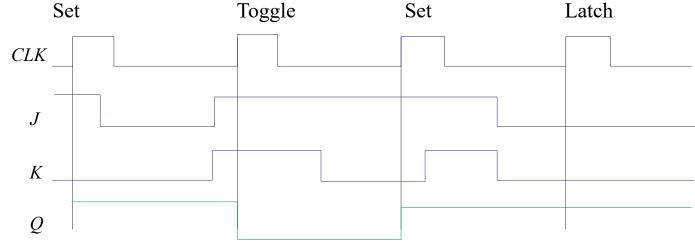

- Edge-triggered J-K flip-flop

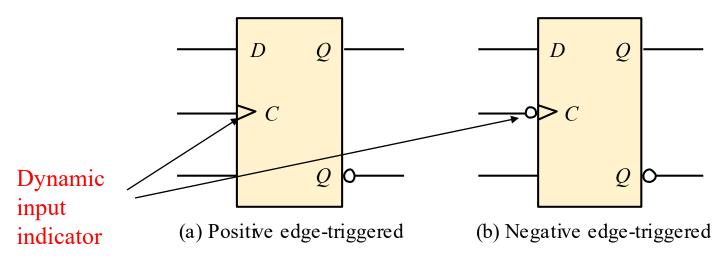

# Flip-flops

A flip-flop differs from a latch in the manner it changes states. A flip-flop is a clocked device, in which only the clock edge determines when a new bit is entered.

The active edge can be positive or negative.

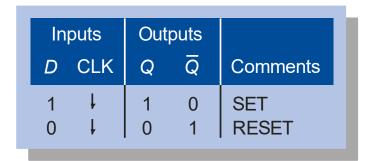

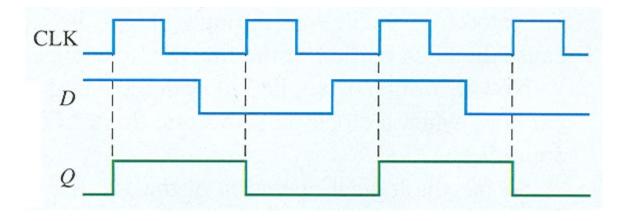

# Flip-flops

The truth table for a positive-edge triggered D flip-flop shows an up arrow to remind you that it is sensitive to its *D* input only on the rising edge of the clock; otherwise it is latched. The truth table for a negative-edge triggered D flip-flop is identical except for the direction of the arrow.

| In | Inputs |   | outs           |          |

|----|--------|---|----------------|----------|

| D  | CLK    | Q | $\overline{Q}$ | Comments |

| 1  | 1      | 1 | 0              | SET      |

| 0  | 1      | 0 | 1              | RESET    |

(a) Positive-edge triggered

(b) Negative-edge triggered

# Edge-triggered D flip-flop

| D III | NPUTS<br>CLK | 00 |   | COMMENTS           |

|-------|--------------|----|---|--------------------|

|       | •            |    |   |                    |

| 1     | 1            | 1  | 0 | SET (stores a 1)   |

| 0     | $\uparrow$   | 0  | 1 | RESET (stores a 0) |

Flip-flops

The J-K flip-flop is more versatile than the D flip flop.

In addition to the clock input, it has two inputs, labeled *J* and *K*. When both *J* and K = 1, the output changes states (toggles) on the active clock edge (in this case, the rising edge).

|   | Inputs |     |                    | puts               |           |

|---|--------|-----|--------------------|--------------------|-----------|

| J | K      | CLK | Q                  | Q                  | Comments  |

| 0 | 0      | †   | $Q_0$              | $\overline{Q}_{0}$ | No change |

| 0 | 1      | 1   | 0                  | 1                  | RESET     |

| 1 | 0      | +   | 1                  | 0                  | SET       |

| 1 | 1      | 1   | $\overline{Q}_{0}$ | $Q_0$              | Toggle    |

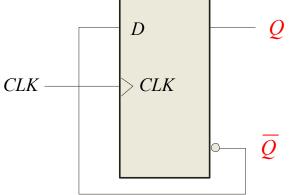

# Flip-flops

A D-flip-flop does not have a toggle mode like the J-K flipflop, but you can hardwire a toggle mode by connecting  $\overline{Q}$ back to D as shown. This is useful in some counters as you will see in Chapter 8.

For example, if Q is LOW,  $\overline{Q}$  is HIGH and the flip-flop will toggle on the next clock edge. Because the flip-flop only changes on the active edge, the output will only change once for each clock

pulse.

Floyd Digital Fundamentals, 9/e

# D flip-flop hardwired for a toggle mode

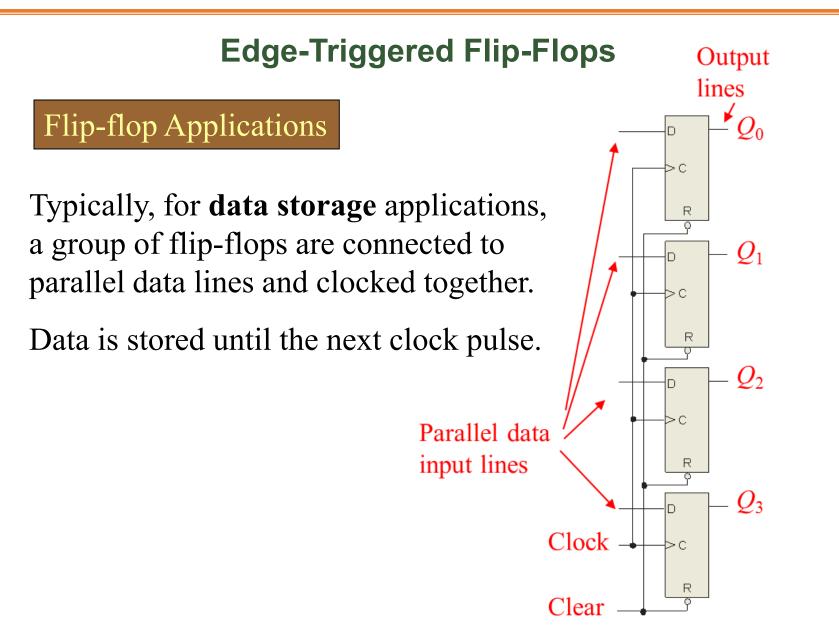

# Flip-flop Applications

Principal flip-flop applications are for temporary data storage, as frequency dividers, and in **Counters** (which are covered in detail in Chapter 8).

# Flip-flop Applications

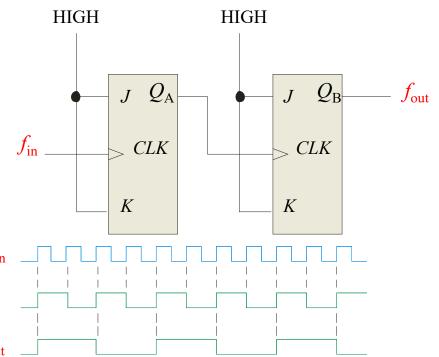

For **frequency division**, it is simple to use a flip-flop in the toggle mode or to chain a series of toggle flip flops to continue to divide by two. HIGH HIGH

One flip-flop will divide  $f_{in}$ by 2, two flip-flops will divide  $f_{in}$  by 4 (and so on). A side benefit of frequency division is that the output has an exact 50% duty cycle.

Waveforms:

- Monostable (One-Shot)

- Astable.

## Monostable

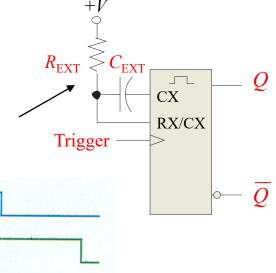

The **monostable** or **one-shot** multivibrator is a device with only one stable state. When triggered, it goes to its unstable state for a predetermined length of time, then returns to its stable state.  $+_{V}$

For most one-shots, the length of time in the unstable state  $(t_W)$  is determined by an external *RC* circuit.

Trigger

Q

## Astable

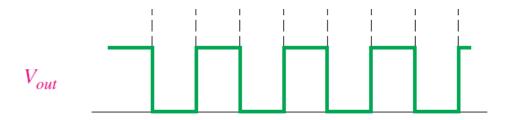

An astable multivibrator is a device that has no stable states; it changes back and forth (oscillates) between two unstable states without any external triggering. The resulting output is typically a square wave that is used as a clock signal in many types of sequential logic circuits.

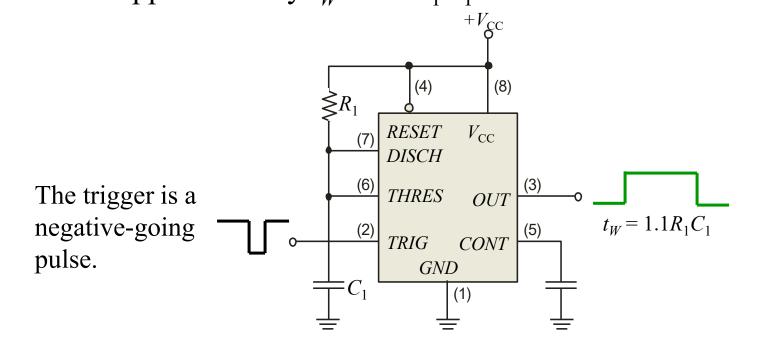

The 555 timer

The 555 timer can be configured in various ways. A basic monostable is shown. The pulse width is determined by  $R_1C_1$  and is approximately  $t_W = 1.1R_1C_1$ .

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

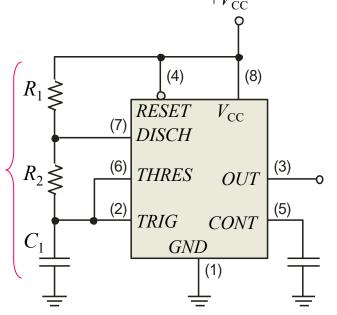

# The 555 timer

The 555 can be configured as a basic astable multivibrator with the circuit shown. In this circuit  $C_1$  charges through  $R_1$ and  $R_2$  and discharges through only  $R_2$ .

The output frequency is given by:

$$f = \frac{1.44}{(R_1 + 2R_2)C_1}$$

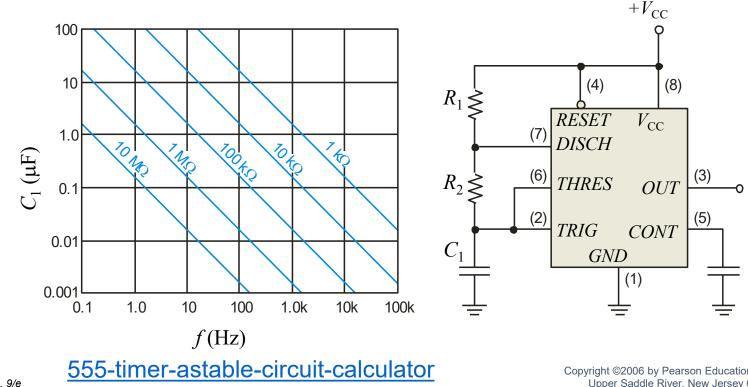

# The 555 timer

Given the components, you can read the frequency from the chart. Alternatively, you can use the chart to pick components for a desired frequency.

Floyd Digital Fundamentals, 9/e Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved

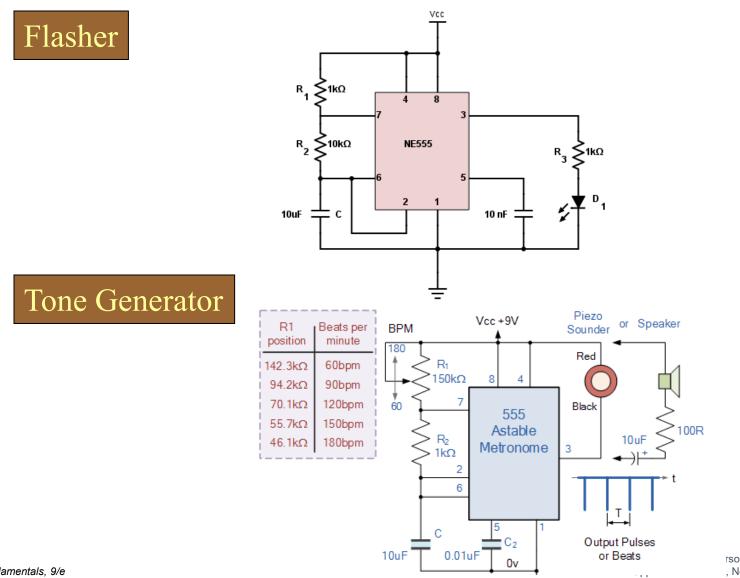

#### **Timer 555 Applications**

rson Education, Inc. , New Jersey 07458 All rights reserved.